Financement de notre regroupement

La direction du ReSMiQ attendait la décision du Fonds de recherche du Québec – Nature et technologies (FRQNT) concernant la demande de renouvèlement de la subvention de notre regroupement stratégique. Le FRQNT nous a récemment communiqué la décision de renouveler la subvention du ReSMiQ pour les 6 prochaines années avec une contribution de 432 000$ annuellement. Lors de ce processus de renouvèlement le ReSMiQ a reçu la plus haute note dans chacun des critères d’évaluation et le plus haut montant alloué par le FRQNT dans le concours 2015-2016. La direction du centre tient à remercier tous ceux qui ont contribué à faire évoluer ReSMiQ et à fournir de l’aide tout le long de la production de cette demande. Plus de détails

Colloque ReSMiQ 2015 à Rimouski

C’est dans le cadre du 83e congrès de l’ACFAS à Rimouski que nous avons organisé notre colloque annuel. C’est avec un grand enthousiasme que nous avons reçu nos conférenciers invités, dont les professeurs Mohamed Bahoura de l’UQAR et Wei Shi de l’Université Laval, ainsi que la quarentaine de participants qui y ont assisté. À cette occasion, dix-sept étudiants du ReSMiQ ont participé au concours d’affiches scientifiques et le comité de sélection a été impressionné par la grande qualité des travaux présentés. De plus, 3 d’entre eux ont bénéficié d’un prix pour récompenser l’excellence de leurs présentations. Nous en profitons pour vous donner rendez-vous lors du prochain congrès de l’ACFAS qui se tiendra à l’UQAM en mai 2016. Voir le programme détaillé

Mini-symposium en microfluidique à l’Université Laval

Nous avons soutenu la demi-journée microfluidique qui s’est tenue à l’Université Laval le 27 mai dernier devant une quarantaine de participants. Organisé par Dr. Miled de l’Université Laval et commandité par CMC Microsystèmes et IEEE Québec dans le but de promouvoir la recherche en microfluidique. Le programme incluait une conférence de marque offerte par Dr. Juncker de McGill, une présentation par B. Mallard de CMC Microsystèmes, une session de présentation d’affiches avec remise de prix et enfin une table ronde sur le sujet. Plus de détails

De gauche à droite: Paul Fortier, Président IEEE-Québec, Amine Miled Co-président du réseau de recherche en microfluidique à l’université Laval et du chapitre IEEE-EMBS/CAS Québec, David Juncker, Conférencier invité de l’Univ. McGill, Jesse Greener, Co-président du réseau de recherche en microfluidique à l’université Laval, Robert Mallard, CMC Microsystèmes.

De gauche à droite: Paul Fortier, Président IEEE-Québec, Amine Miled Co-président du réseau de recherche en microfluidique à l’université Laval et du chapitre IEEE-EMBS/CAS Québec, David Juncker, Conférencier invité de l’Univ. McGill, Jesse Greener, Co-président du réseau de recherche en microfluidique à l’université Laval, Robert Mallard, CMC Microsystèmes.

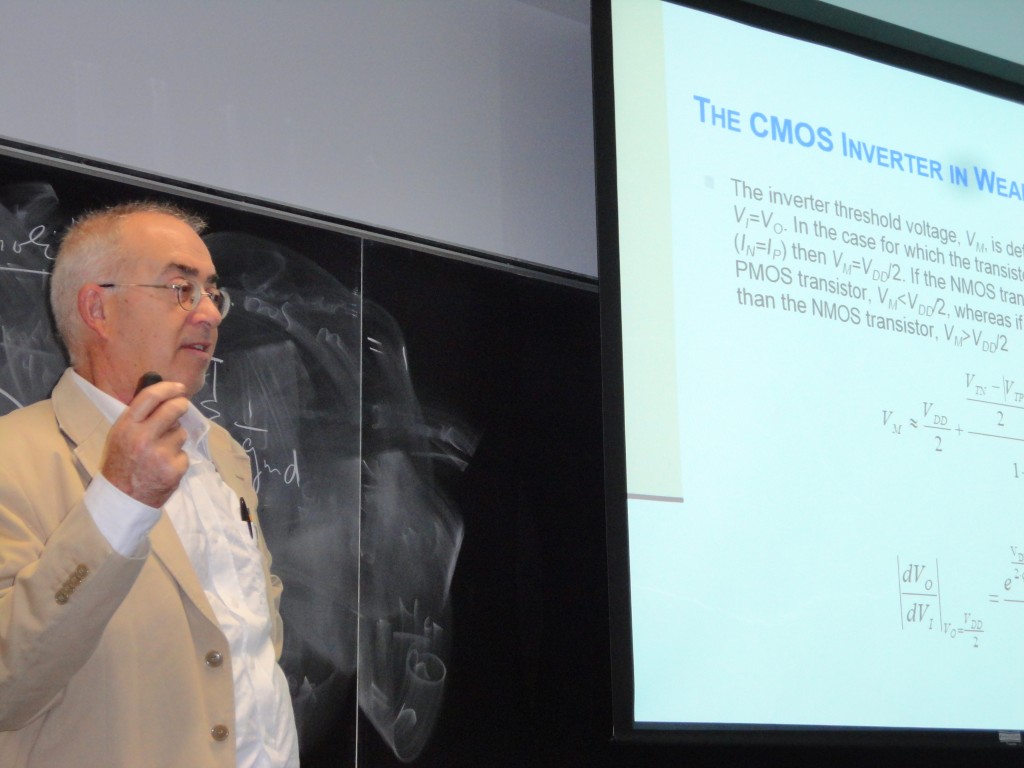

Cours intensif ReSMiQ

Carlos Galup Montoro de l’Universidade Federal de Santa Catarina au Brésil a présenté le cours intensif intitulé «Ultra-Low-Voltage (ULV) IC Design» à Polytechnique Montréal dans le cadre de nos activités de formation en collaboration avec les chapitres IEEE de Montréal des sociétés Solid State Circuits (SSC) et Circuits and Systems (CAS). Voir le résumé de la présentation

Carlos Galup Montoro de l’Universidade Federal de Santa Catarina au Brésil a présenté le cours intensif intitulé «Ultra-Low-Voltage (ULV) IC Design» à Polytechnique Montréal dans le cadre de nos activités de formation en collaboration avec les chapitres IEEE de Montréal des sociétés Solid State Circuits (SSC) et Circuits and Systems (CAS). Voir le résumé de la présentation

NOUVELLES DES MEMBRES

Rayonnement

– Dr. Sawan de Polytechnique a offert deux conférences de marques lors de la 6e conférence MCETECH (Montréal) et de la conférence CIIA’2015 (Algérie).

Détails pour MCETECH / Détails pour CIIA’2015

Réussites

– Dr. Fréchette de l’Université de Sherbrooke dirige les travaux d’Andréane D’Arcy-Lepage et de Mahmood R. S. Shirazi qui ont respectivement remporté le second prix lors de la compétition d’affiche pour étudiant du 1er cycle et le prix du choix du public de l’ASME-IMECE 2014 tenu à Montréal.

– Dr. Sawan de Polytechnique Montréal à reçu le prix Shanghai Municipality International Collaboration Award. Plus de détails

– Dr. Gosselin et Dr. Shi de l’université Laval et Dr. Sawan et Dr. Savaria de Polytechnique Montréal ainsi que 4 autres collègues obtiennent le financement de la Fondation canadienne pour l’innovation pour le développement d’infrastructures de recherche partagées à l’Université Laval.

– Dr. Izquierdo, Dr. Deslandes, Dr. Nabki and Dr. Boukadoum de l’Université du Québec à Montréal obtiennent le financement de la fondation canadienne pour l’innovation pour le projet « Plateforme pour la conception, la caractérisation et l’intégration de dispositifs nanoscopiques dans des microsystèmes ».

– Dr. Massicotte de l’Université du Québec à Trois-Rivières obtient une subvention ENGAGE du CRSNG avec Simaudio.com.

– Dr. Gosselin et Dr. Miled de l’université Laval ont été récompensé du prix du meilleur chapitre 2015 de la société IEEE Engineering in Medicine & Biology.

ACTIVITÉS DU RESMIQ

Bourses et prix

– Concours de démonstration technique (JIR2015)

Les étudiants de premier cycle et de cycles supérieurs des institutions d’enseignement ou d’un collège/CEGEP du Québec sont invités à participer au prochain concours dans le cadre de la 4e édition de la journée de l’innovation en soumettant leur projet. Plus de 5000$ en prix à gagner.

DATE LIMITE DE DÉPÔT: 10 juin 2015

Plus de détails

SIGNAL est le principal outil de diffusion de nouvelles du Regroupement Stratégique en Microsystèmes du Québec (ReSMiQ). Ce bulletin se veut un lien entre les membres du ReSMiQ et toute autre personne intéressée par la recherche et l’innovation dans le domaine des microsystèmes. Nous nous engageons à valoriser les travaux de nos membres et augmenter la visibilité du ReSMiQ.

ReSMiQ est un regroupement de chercheurs au sein d’un centre de recherche interuniversitaire qui peut compter sur le soutien du Fonds de recherche du Québec – Nature et technologies (FRQNT) et de dix (10) universités québécoises impliquées dans la recherche sur les microsystèmes.

Le Pr Claude Thibeault a reçu le doctorat en Génie électrique de l'École Polytechnique de Montréal, Canada. Il est actuellement professeur titulaire au Département de génie électrique de l'École de technologie supérieure à Montréal, Canada. Il a dirigé avec succès plusieurs projets de recherche supportés par l'industrie pour développer des prototypes et des produits de communication sans fil, de vidéo numérique et de détection radar, entre autres. Ses intérêts de recherche portent sur les méthodologies de conception et vérification de ciblant les ASIC et FPGA, l’effet des radiations, les stratégies de tolérance aux défectuosités, ainsi que les tests et diagnostics de circuits intégrés basés sur le courant. Il détient 13 brevets et a publié plus de 130 articles de revues et conférences avec comité de lecture, qui ont été cités plus de 730 fois. Il est coauteur d’articles qui ont été sélectionnés comme les meilleurs dans leur catégorie lors des conférences internationales. Le Pr Thibeault a été membre du comité organisateur dans diverses conférences, dont le IEEE VLSI Test Symposium, pour lequel il a été le président du programme en 2010-2012, et le président général en 2014-2015.

Le Pr Claude Thibeault a reçu le doctorat en Génie électrique de l'École Polytechnique de Montréal, Canada. Il est actuellement professeur titulaire au Département de génie électrique de l'École de technologie supérieure à Montréal, Canada. Il a dirigé avec succès plusieurs projets de recherche supportés par l'industrie pour développer des prototypes et des produits de communication sans fil, de vidéo numérique et de détection radar, entre autres. Ses intérêts de recherche portent sur les méthodologies de conception et vérification de ciblant les ASIC et FPGA, l’effet des radiations, les stratégies de tolérance aux défectuosités, ainsi que les tests et diagnostics de circuits intégrés basés sur le courant. Il détient 13 brevets et a publié plus de 130 articles de revues et conférences avec comité de lecture, qui ont été cités plus de 730 fois. Il est coauteur d’articles qui ont été sélectionnés comme les meilleurs dans leur catégorie lors des conférences internationales. Le Pr Thibeault a été membre du comité organisateur dans diverses conférences, dont le IEEE VLSI Test Symposium, pour lequel il a été le président du programme en 2010-2012, et le président général en 2014-2015.